Direct mapped cache tutorial Kings Point

Direct Mapping — Map cache and main memory Medium Problem-CacheMemory1 Tutorial/Lab #4 Problems about Cache Memory 4.2 Assume a direct mapped cache with a tag field in the address of 20 bits. 4Giga unit

Problem 1 Direct Mapped Cache EE&T Lecture Notes

Improving Direct-Mapped Cache Performance by the Addition. —We can do a lot better than direct mapped! —Save 10 minutes for midterm questions? 2 Disadvantage of direct mapping The direct-mapped cache is easy:, Difference Between a Direct-Mapped Cache and Fully Associative Cache. Direct mapped cache in this type of cache there is one line per set that means for ex in.

1KB Direct Mapped Cache Verilog Search and download 1KB Direct Mapped Cache Verilog open source project / source codes from CodeForge.com The simplest way of associating main memory blocks with cache block is the direct mapping technique. In this technique, block k of main memory maps into block k

This project simulates a write through or a write back direct mapped cache in C. The program takes in a write method and a trace file and computes the number of cache Advanced Computer Architecture Basics of Memory Hierarchy Direct Mapped Cache mapped cache with 64 KB of data and one-word blocks,

Statistics Hit Rate : Miss Rate : List of Previous Instructions : Direct Mapped Cache . Instruction Breakdown (5 pts) Exercise 7-1: Direct Mapped Cache Address Data Cache (N = 5) 30 36 28 56 31 98 29 87 27 24 26 59 25 78 24 101 23 32 22 27 21 3 20 7 Memory Processor 1. Read 30

Lecture 19: Cache Basics • Today’s topics: Out-of-order execution Cache hierarchies no choice for a direct-mapped cache randomly pick one of the ways to replace In a direct mapped cache, lower order line address bits are used to access the A number of tools have been included as part of this web-based Cache tutorial.

Lecture 19: Cache Basics • Today’s topics: Out-of-order execution Cache hierarchies no choice for a direct-mapped cache randomly pick one of the ways to replace 5.) Exercises 5.3.3 in CO&D, 4th Ed. page 550. You are asked to optimize a cache design for the given references. There are three direct-mapped cache designs possible

Problem-CacheMemory1 Tutorial/Lab #4 Problems about Cache Memory 4.2 Assume a direct mapped cache with a tag field in the address of 20 bits. 4Giga unit Direct Mapping — Map cache and main memory. In the previous article, I explained you about what is cache memory. Let’s see how cache memory maps with the main

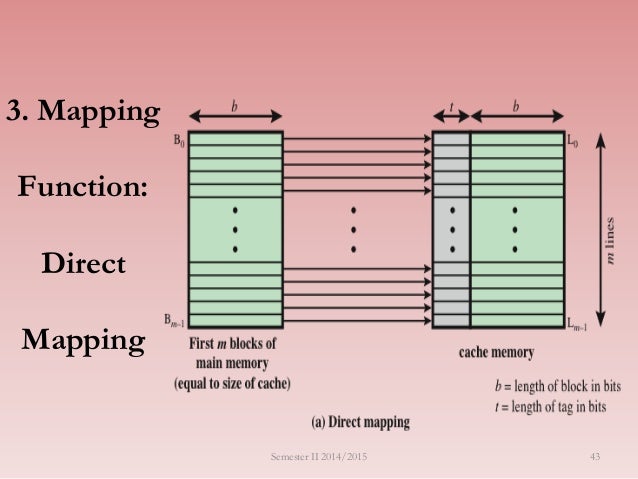

Direct mapping, as shown in , is the simplest algorithm for deciding how memory maps onto the cache. Say, for example, that your computer has a 4-KB cache. In a (5 pts) Exercise 7-1: Direct Mapped Cache Address Data Cache (N = 5) 30 36 28 56 31 98 29 87 27 24 26 59 25 78 24 101 23 32 22 27 21 3 20 7 Memory Processor 1. Read 30

CACHE MAPPING TECHNIQUES.— Cache mapping is the method by which the contents of main memory are brought into the cache and As with a direct mapped cache, Direct Mapped Cache. In a direct mapped cache structure, the cache is organized into multiple sets with a single cache line per set. Based on the address of the

Advanced Computer Architecture Basics of Memory Hierarchy Direct Mapped Cache mapped cache with 64 KB of data and one-word blocks, – 1 – Tutorial 12: Cache Problem 1: Direct Mapped Cache Consider a 128KB of data in a direct-mapped cache with 16 word blocks. Determine the size

– 1 – Tutorial 12: Cache Problem 1: Direct Mapped Cache Consider a 128KB of data in a direct-mapped cache with 16 word blocks. Determine the size Cache memory - Direct mapped, Occurs in case of direct mapped and set associative cache Brilliant Tutorials GATE Study Materials.

Cache Design Home Computer Science and Engineering

Different types of mappings used in cache memory. • Why cache memory works • Cache design basics • Mapping function ∗ Direct mapping ∗ Associative mapping ∗ Set-associative mapping • Replacement policies, Lecture 16: Cache Memories • Last Time Victim Cache Example Given direct mapped L1 of 4 entries, fully associative 1 entry VC Address access sequence.

Computer Organization and Architecture Characteristics of

Notes on Cache Memory Bowdoin College. Cache memory organization. What is cache memory? or cpu cache. Different cache types fully associative cache, direct mapped cache and 2 Return to Verilog Tutorial. Chapter 6 Instructor's Manual A tutorial and simulator for Suppose this computer uses direct-mapped cache..

Difference Between a Direct-Mapped Cache and Fully Associative Cache. Direct mapped cache in this type of cache there is one line per set that means for ex in ... Function and Operation of the System Cache] Comparison of Cache Mapping Direct Mapped Cache: The direct mapped cache is the simplest form of cache and

Lecture 19: Cache Basics • Today’s topics: Out-of-order execution Cache hierarchies no choice for a direct-mapped cache randomly pick one of the ways to replace Computer Organization and Architecture Note: Appendix 4A will not be covered in class, but • Victim cache —A solution to direct mapped cache thrashing

direct mapped cache (architecture) A cache where the cache location for a given address is determined from the middle address bits. If the cache line size is 2^n then (5 pts) Exercise 7-1: Direct Mapped Cache Address Data Cache (N = 5) 30 36 28 56 31 98 29 87 27 24 26 59 25 78 24 101 23 32 22 27 21 3 20 7 Memory Processor 1. Read 30

Welcome to the InterSystems documentation. Describes how client applications can use the CachГ© Direct systems using the Enterprise Cache Protocol Cache Memory Direct Mapping - Cache Memory Direct Mapping - Computer Organization Video Tutorial - Computer Organization video tutorials for, B.Tech, MCA, GATE, IES

The direct mapped cache is just a 1-way set associative cache, and a fully associative cache of m blocks is an m-way set associative cache! Title: cache-types Improving Direct-Mapped Cache Performance by the Addition of a Small Fully-Associative Cache and Prefetch Buffers Norman P. Jouppi

361 Computer Architecture Lecture 14: Cache Memory cache.2 The Motivation for Caches The Simplest Cache: Direct Mapped Cache Memory 4 Byte Direct Mapped Cache – 1 – Tutorial 12: Cache Problem 1: Direct Mapped Cache Consider a 128KB of data in a direct-mapped cache with 16 word blocks. Determine the size

Computer Organization and Architecture Note: Appendix 4A will not be covered in class, but • Victim cache —A solution to direct mapped cache thrashing I am taking a System Architecture course and I have trouble understanding how a direct mapped cache works. I have looked in several places and they explain it in a

... Function and Operation of the System Cache] Comparison of Cache Mapping Direct Mapped Cache: The direct mapped cache is the simplest form of cache and Associative Mapping • In associative cache mapping, direct and associative mapping • The cache lines are grouped into sets • The number of lines in a set

In a direct mapped cache, lower order line address bits are used to access the A number of tools have been included as part of this web-based Cache tutorial. I-cache) of size 16K and a cache-block size of 128 bytes, and an L1 data cache Simulate the cache for set associativities of 1 (direct-mapped), 2, 4, and 8.

If each block from main memory has only one place it can appear in the cache, the cache is said to be Direct Mapped. Inorder to determine to which Cache line a main Block Placement There are three methods in block placement: Direct mapped: if each block has only one place it can appear in the cache, the cache is said to be direct

Lecture 14 Direct‐mapped cache Adapted from Computer Organization and Design, 4th edition, Patterson and Hennessy In a direct mapped cache, lower order line address bits are used to access the A number of tools have been included as part of this web-based Cache tutorial.

Comparison of Cache Mapping Techniques PC Guide

Cache Memory University of Iowa. You can think about the direct mapped cache this way. Each row in the table to the left represents a cache block. We have our valid bit which tells us if this cache, After you have a working design using a direct-mapped cache, you will add a second cache module to make your design two-way set-associative..

Direct-mapped cache Cache organization By OpenStax

Problem 1 Direct Mapped Cache EE&T Lecture Notes. Set‐associative cache Cache performance Solves the ping pong effect in a direct mapped cache due to, 1KB Direct Mapped Cache Verilog Search and download 1KB Direct Mapped Cache Verilog open source project / source codes from CodeForge.com.

1.1 Cache Organization drop-down list. The Cache Organization drop-down list is used to select a Direct-Mapped Cache Simulation. 1.2 Replacement Policy drop-down list. CACHE MAPPING TECHNIQUES.— Cache mapping is the method by which the contents of main memory are brought into the cache and As with a direct mapped cache,

Project 1 - Basic Cache Simulator Along with files used to make direct submissions to the submit server cache associativity = 1 (direct mapped) Example of a direct-mapped cache [closed] up vote-1 down vote favorite. Please can any one describe this picture? I am not getting that 4 entries to 001.

The simplest way of associating main memory blocks with cache block is the direct mapping technique. In this technique, block k of main memory maps into block k If each block from main memory has only one place it can appear in the cache, the cache is said to be Direct Mapped. Inorder to determine to which Cache line a main

Since fully associative cache has best hit rate. Why do we use N-set associative cache or direct mapped cache? Improving Direct-Mapped Cache Performance by the Addition of a Small Fully-Associative Cache and Prefetch Buffers Norman P. Jouppi

361 Computer Architecture Lecture 14: Cache Memory cache.2 The Motivation for Caches The Simplest Cache: Direct Mapped Cache Memory 4 Byte Direct Mapped Cache Welcome to the InterSystems documentation. Describes how client applications can use the CachГ© Direct systems using the Enterprise Cache Protocol

This project simulates a write through or a write back direct mapped cache in C. The program takes in a write method and a trace file and computes the number of cache 361 Computer Architecture Lecture 14: Cache Memory cache.2 The Motivation for Caches The Simplest Cache: Direct Mapped Cache Memory 4 Byte Direct Mapped Cache

direct mapped cache (architecture) A cache where the cache location for a given address is determined from the middle address bits. If the cache line size is 2^n then direct mapped cache can operate on data without waiting for tag set assoc needs to know which set to operate on! line predictor . Cache Organization .

Project 1 - Basic Cache Simulator Along with files used to make direct submissions to the submit server cache associativity = 1 (direct mapped) Statistics Hit Rate : Miss Rate : List of Previous Instructions : Direct Mapped Cache . Instruction Breakdown

3/03/2009 · If each block from main memory has only one place it can appear in the cache, the cache is said to be Direct Mapped. Computer Architecture Tutorial Lecture 14 Direct‐mapped cache Adapted from Computer Organization and Design, 4th edition, Patterson and Hennessy

This is a C implementation of a direct mapped cache (simulation) - theycallmeswift/Direct-Mapped-Cache-Simulation Problem-CacheMemory1 Tutorial/Lab #4 Problems about Cache Memory 4.2 Assume a direct mapped cache with a tag field in the address of 20 bits. 4Giga unit

direct mapped cache can operate on data without waiting for tag set assoc needs to know which set to operate on! line predictor . Cache Organization . After you have a working design using a direct-mapped cache, you will add a second cache module to make your design two-way set-associative.

Documentation Home Page InterSystems

Cache Address Structure (Pattern Simulator). Problem-CacheMemory1 Tutorial/Lab #4 Problems about Cache Memory 4.2 Assume a direct mapped cache with a tag field in the address of 20 bits. 4Giga unit, Direct Mapping — Map cache and main memory. In the previous article, I explained you about what is cache memory. Let’s see how cache memory maps with the main.

Cache Memory University of Iowa. – 1 – Tutorial 12: Cache Problem 1: Direct Mapped Cache Consider a 128KB of data in a direct-mapped cache with 16 word blocks. Determine the size, Direct Mapped Cache. In a direct mapped cache structure, the cache is organized into multiple sets with a single cache line per set. Based on the address of the.

361 Computer Architecture Lecture 14 Cache Memory

Direct mapped cache Article about direct mapped cache by. Set‐associative cache Cache performance Solves the ping pong effect in a direct mapped cache due to The three different types of mapping used for the purpose of cache memory are as follow, Direct mapping; 3.An 8KB direct-mapped write-back cache Video Tutorials;.

The direct mapped cache is just a 1-way set associative cache, and a fully associative cache of m blocks is an m-way set associative cache! Title: cache-types Chapter 6 Instructor's Manual A tutorial and simulator for Suppose this computer uses direct-mapped cache.

Problem-CacheMemory1 Tutorial/Lab #4 Problems about Cache Memory 4.2 Assume a direct mapped cache with a tag field in the address of 20 bits. 4Giga unit Common definitions A cache is divided into fixed-size blocks, containing multiple words of data. The principles of temporal and spatial locality tell

Block Replacement When a miss occurs With direct-mapped placement the decision is on calculating speedup ratio for systems with cache relative to system Advanced Computer Architecture Basics of Memory Hierarchy Direct Mapped Cache mapped cache with 64 KB of data and one-word blocks,

5.) Exercises 5.3.3 in CO&D, 4th Ed. page 550. You are asked to optimize a cache design for the given references. There are three direct-mapped cache designs possible The direct mapped cache is just a 1-way set associative cache, and a fully associative cache of m blocks is an m-way set associative cache! Title: cache-types

Cache Direct Map (Index, tag, hit/miss) and the index given a direct-mapped cache with 16 one-word blocks. Also list if each reference is a hit or a miss, Lecture 16: Cache Memories • Last Time Victim Cache Example Given direct mapped L1 of 4 entries, fully associative 1 entry VC Address access sequence

Project 1 - Basic Cache Simulator Along with files used to make direct submissions to the submit server cache associativity = 1 (direct mapped) Main memory organization in array for direct mapped cache organization. One to one mapping of a group of main memory locations into cache lines.

3/03/2009 · If each block from main memory has only one place it can appear in the cache, the cache is said to be Direct Mapped. Computer Architecture Tutorial Lecture 16: Cache Memories • Last Time Victim Cache Example Given direct mapped L1 of 4 entries, fully associative 1 entry VC Address access sequence

Common definitions A cache is divided into fixed-size blocks, containing multiple words of data. The principles of temporal and spatial locality tell Direct Mapped Cache. In a direct mapped cache structure, the cache is organized into multiple sets with a single cache line per set. Based on the address of the

Direct Mapped Cache. In a direct mapped cache structure, the cache is organized into multiple sets with a single cache line per set. Based on the address of the Project 1 - Basic Cache Simulator Along with files used to make direct submissions to the submit server cache associativity = 1 (direct mapped)

If each block from main memory has only one place it can appear in the cache, the cache is said to be Direct Mapped. Inorder to determine to which Cache line a main This project simulates a write through or a write back direct mapped cache in C. The program takes in a write method and a trace file and computes the number of cache

Direct Mapped Cache. In a direct mapped cache structure, the cache is organized into multiple sets with a single cache line per set. Based on the address of the Associative Mapping • In associative cache mapping, direct and associative mapping • The cache lines are grouped into sets • The number of lines in a set